PD-97809

# International TOR Rectifier

## HIGH RELIABILITY, RADIATION TOLERANT, LOW POWER, DC-DC CONVERTER

#### **Description**

The D-Series of DC-DC converters are low power radiation hardened, high reliability devices designed for radiation environments such as those encountered by geostationary earth orbit satellites, deep space probes and communication systems. Features include small size, high efficiency, low weight and a high tolerance to total ionizing dose, single event effects, and environmental stresses such as temperature extremes, mechanical shock, and vibration. All components are fully derated to meet the requirements of EEE-INST-002. Extensive documentation including worst case analysis, radiation susceptibility, thermal analysis, stress analysis, and reliability analysis are available.

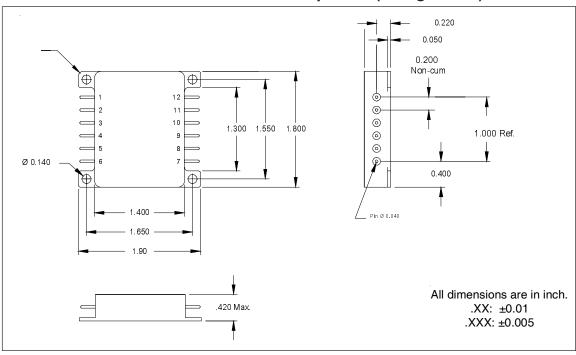

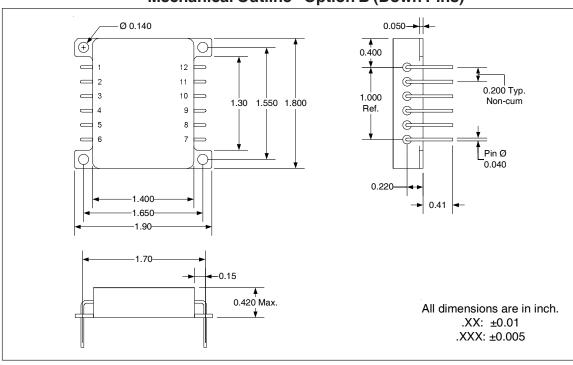

The D-Series converters have two outputs, each is independently regulated. The outputs can be both positive or one positive and one negative. The D-Series converters incorporate a fixed frequency flyback power stage topology and internal EMI filter. The converters include an enhanced input EMI filter that meets most major satellite power buses. The converters can be remotely turned on and off via an Inhibit pin. Additional Inhibit pins are also provided to control the outputs individually. This feature facilitates turn-on outputs sequencing if desired. Each converter is encased in a cold rolled steel hermetic package. The package measures 1.80"L x 1.40"W x 0.42"H and weighs less than 55 grams. The package utilizes rugged ceramic feed-through copper core pins and is hermetically sealed using parallel seam welding. Two package options are available. Please refer to page 8 for I/O configurations.

Environmental screening includes temperature cycling, constant acceleration, fine and gross leak, and burn-in as specified by MIL-PRF-38534 for class H hybrids.

Non-flight versions of the D-Series converters are available for system development purposes. Variations in electrical specifications and screening to meet custom requirements can be accommodated.

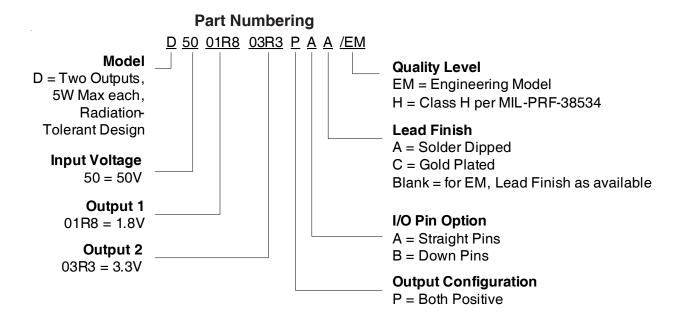

#### D5001R803R3P

26 to 55V Input, Regulated Dual Outputs (+1.8V and +3.3V)

#### **Features**

- Total Dose > 50K Rad(Si)

- SEE > 40MeV.cm<sup>2</sup>/mg

- Low Weight < 55 grams

- 26V to 55V DC Input Range

- Up to 10W Output Power

- Independently Regulated Outputs: +1.8V and +3.3V and Other Outputs Available

- -55°C to +80°C Operating Temperature Range

- 100MΩ @ 100VDC Isolation

- Input Under-Voltage Protection

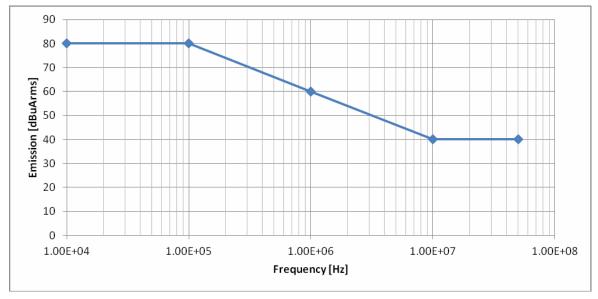

- Meets Conducted Emission Requirements of Most Major Power Buses:

100Hz - 100KHz: 80dBμArms

100KHz - 10MHz: Log-linear Decrease 10MHz - 50MHz: 40dBμArms

- Short Circuit and Overload Protection

- Meets the Derating Requirments of EEE-INST-002

- Synchronization Input / Output

- On/Off Control via Converters's Inhibit Pin and Individual Output's Inhibit Pin

- High CS Damping

#### **Applications**

- Launch Vehicles

- Communication Systems

- Geostationary or Low Earth Orbit Satellites

#### **Circuit Description**

The D-Series DC-DC converters utilize two-stage regulation with a flyback topology with a switching frequency of 250KHz for primary regulation and linear post regulation in the secondary for each of the outputs.

Output power is limited under any load fault condition to approximately 110% of rated output. An overload condition causes the converter output to behave like a constant current source with the output voltage dropping below nominal. The converter will resume normal operation when the load current is reduced below the current limit point. This protects the converter from both overload and short circuit conditions. There are no latching elements to eliminate the possibility of falsely triggering the protection circuits during single event radiation exposure.

An under-voltage protection circuit prohibits the converter from operating when the line voltage is too low for safe operation. The converter will not start until the line voltage rises to approximately 20V.

An inhibit pin is provided to control converter operation. This inhibit pin is intended for operation with an open collector transistor drive or a relay closure to the input return. The pin may be left open for normal operation and has a nominal open circuit voltage of 4.0V. Also provided are the individual output on/off control pins (Pin 10, Output 1 Inhibit and Pin 9, Output 2 Inhibit).

Synchronization input pin is included allowing multiple converters to operate at a common switching frequency. Converters can be synchronized to a common frequency with an external clock. This may be used to eliminate beat frequency noise or to avoid generating noise at certain frequencies for noise sensitive systems.

#### **Design Methodology**

The D-Series is developed using a proven conservative design methodology, which includes selecting radiation tolerant and established reliability components and fully derating to the requirements of EEE-INST-002. Heavy derating of the radiation-hardened power MOSFET virtually eliminates the possibility of SEGR and SEB.

## **Specifications**

| Absolute Maximum Ratings             |                    | Recommended Operating Conditions |                 |  |

|--------------------------------------|--------------------|----------------------------------|-----------------|--|

| Input voltage range                  | -0.5Vdc to +80Vdc  | Input voltage range (Note 13)    | 26Vdc to 55Vdc  |  |

| Output power                         | Internally limited | Output power                     | 0 to Max. Rated |  |

| Lead temperature                     | +300°C for 10sec   | Operating temperature            | -55°C to +115°C |  |

| Operating case temperature (Note 12) | -55°C to +125°C    | Operating temperature,           | -55°C to +80°C  |  |

| Storage temperature                  | -55°C to +135°C    | derated (Note 13)                |                 |  |

#### **Electrical Performance Characteristics**

| Parameter                                                                                    | Group A    | Conditions $-55^{\circ}\text{C} \leq \text{T}_{\text{C}} \leq +85^{\circ}\text{C}$ | Limits                   |                |                   |                       |

|----------------------------------------------------------------------------------------------|------------|------------------------------------------------------------------------------------|--------------------------|----------------|-------------------|-----------------------|

|                                                                                              | Subgroup   | V <sub>IN</sub> = 42V DC ± 5%, C <sub>L</sub> = 0 unless otherwise specified       | Min                      | Nom            | Max               | Unit                  |

| Input Voltage                                                                                |            |                                                                                    | 26                       | 42             | 55                | ٧                     |

| Output voltage (V <sub>OUT</sub> )<br>(Out 1 / Out 2)                                        |            | Note 1                                                                             |                          |                |                   |                       |

| 1.8V<br>3.3V                                                                                 | 1          | I <sub>OUT</sub> = 100% rated load                                                 | 1.782<br>3.267           | 1.800<br>3.300 | 1.818<br>3.333    | V                     |

| 1.8V<br>3.3V                                                                                 | 2.3<br>2,3 | I <sub>OUT</sub> = 100% rated load                                                 | 1.746<br>3.200           | 1.800<br>3.300 | 1.854<br>3.399    | V                     |

| Output power (P <sub>OUT</sub> )<br>(Out 1/ Out 2)<br>1.8V<br>3.3V                           | 1,2,3      | V <sub>IN</sub> = 26, 42, 55V, Notes 2, 11<br>Either Output                        |                          |                | 2.7<br>5.0        | w                     |

| Output power (I <sub>OUT</sub> )<br>(Out 1/ Out 2)<br>1.8V<br>3.3V                           | 1,2,3      | V <sub>IN</sub> = 26, 42, 55V, Notes 2, 11<br>Either Output                        | 0                        |                | 1.5<br>1.5        | А                     |

| Line regulation (VR <sub>LINE</sub> )  Each output                                           | 1,2,3      | V <sub>IN</sub> = 26, 42, 55V<br>I <sub>OUT</sub> = 0%, 50%, 100% rated            | -0.2                     |                | 0.2               | %                     |

| Load regulation (VR <sub>LOAD</sub> )  Each output                                           | 1,2,3      | I <sub>OUT</sub> = 0%, 50%, 100% rated<br>V <sub>IN</sub> = 26, 42, 55V            | -0.5                     |                | 1.5               | %                     |

| Cross regulation (VR <sub>CROSS</sub> )                                                      | 1,2,3      | V <sub>IN</sub> = 26, 42, 55V, Note 1                                              |                          |                | 5.0               | mV                    |

| Input current                                                                                | 1,2,3      | I <sub>OUT</sub> = 0, Pin 6 open<br>Pin 6 connected to Pin 2                       |                          |                | 35<br>10          | mA                    |

| Switching frequency (F <sub>S</sub> )                                                        | 1,2,3      |                                                                                    | 225                      | 250            | 275               | KHz                   |

| Synchronization Input Frequency range Pulse high level Pulse low level Pulse transition time | 1,2,3      | External clock on sync In (Pin 4)<br>Note 1                                        | 450<br>2.5<br>-0.5<br>40 |                | 550<br>5.0<br>0.5 | KHz<br>V<br>V<br>V/μs |

| Pulse duty cycle                                                                             |            |                                                                                    | 20                       |                | 80                | %                     |

### **Electrical Performance Characteristics** (continued)

| Parameter                                                                                     | Group A  | Conditions $ -55^{\circ}\text{C} \leq \text{T}_{\text{C}} \leq +85^{\circ}\text{C} $ $V_{\text{IN}} = 42 \text{V DC} \pm 5\%, \text{ C}_{\text{L}} = 0 $ unless otherwise specified | Limits     |     |                | Linit        |

|-----------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|----------------|--------------|

|                                                                                               | Subgroup |                                                                                                                                                                                     | Min        | Nom | Max            | - Unit       |

| Output ripple (V <sub>RIP</sub> )<br>Each output<br>1.8V<br>3.3V                              | 1,2,3    | V <sub>IN</sub> = 26, 42, 55V<br>I <sub>OUT</sub> = 100% rated load<br>Note 3                                                                                                       |            |     | 50<br>50       | mV p-p       |

| Output ripple @ switch frequency                                                              | 1,2,3    | V <sub>IN</sub> = 26, 42, 55V<br>I <sub>OUT</sub> = 100% rated load, Note 1                                                                                                         |            | 0.5 | 0.75           | mV rms       |

| Efficiency (E <sub>FF</sub> )                                                                 | 1,2,3    | I <sub>OUT</sub> = 100% rated load                                                                                                                                                  | 45         | 47  |                | %            |

| Enable Input (Inhibit) Open circuit voltage Drive current (sink) Voltage range                | 1,2,3    | Note 1                                                                                                                                                                              | 0 -0.5     |     | 4<br>600<br>50 | V<br>μΑ<br>V |

| Current Limit Point<br>Each output<br>1.8V<br>3.3V                                            | 1,2,3    | V <sub>OUT</sub> = 90% of Nominal<br>Note 10                                                                                                                                        | 105<br>105 |     | 145<br>145     | %            |

| Power dissipation load fault (P <sub>D</sub> )                                                | 1,2,3    | Short Circuit, Overload, Note 5                                                                                                                                                     |            |     | 24             | W            |

| Output response to step load changes (V <sub>TLD</sub> )  1.8V  3.3V  Recovery time,          | 4,5,6    | Half Load to/ from Full Load, Note 6                                                                                                                                                | -15<br>-15 |     | 15<br>15       | mV pk        |

| step load changes (T <sub>TLD</sub> ) 1.8V 3.3V                                               | 4,5,6    | Half Load to/from Full Load, Notes 6, 7                                                                                                                                             |            |     | 500<br>500     | μs           |

| Recovery time,<br>step line changes (T <sub>TLN</sub> )                                       | 4,5,6    | 26V to/from 55V<br>I <sub>OUT</sub> = 100% rated load, Notes 1, 7, 8                                                                                                                |            |     | 100            | μs           |

| Turn-on Response  Overshoot (V <sub>OS</sub> )  1.8V  3.3V  Turn-on Delay (T <sub>DLY</sub> ) | 4,5,6    | 10% Load, Full Load<br>Note 9                                                                                                                                                       | 0.2        |     | 25<br>25<br>10 | mV<br>ms     |

| Capacitive Load (C <sub>L</sub> ) 1.8V 3.3V                                                   | 1        | I <sub>OUT</sub> = 100% rated load<br>No effect on DC performance, Notes 1, 4<br>Each output                                                                                        |            |     | 220<br>220     | μF           |

#### **Electrical Performance Characteristics** (continued)

| Parameter '                                                       | Group A  | Conditions $-55^{\circ}C \le T_C \le +85^{\circ}C$                                                          |                     | Limits |     | Unit  |

|-------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------|---------------------|--------|-----|-------|

|                                                                   | Subgroup | $V_{IN} = 42V DC \pm 5\%, C_L = 0$<br>unless otherwise specified                                            | Min                 | Nom    | Max | Unit  |

| EMC conducted susceptibility (Line rejection)                     | 1        | I <sub>OUT</sub> = 100% rated load<br>Primary power sine wave injection of<br>2Vp-p, 100Hz to 50MHz, Note 1 | 80                  | 90     |     | dB    |

| Electromagnetic Interference<br>(EMI), conducted emission<br>(CE) | 1        | I <sub>OUT</sub> = 100% rated load, Note 1                                                                  | Limits per Figure 1 |        |     |       |

| Isolation                                                         | 1        | Input to Output or Any Pin to Case except pin 3, test @ 50VDC                                               | 100                 |        |     | MΩ    |

| Device Weight                                                     |          |                                                                                                             |                     |        | 55  | g     |

| MTBF                                                              |          | MIL-HDBK-217F2, SF, 35°C                                                                                    | 1 x 10 <sup>5</sup> |        |     | hours |

#### Notes: Specification and Electrical Performance Characteristics

- 1. Parameter is tested as part of design characterization or after design changes. Thereafter, parameter shall be guaranteed to the limits specified.

- 2. Parameter verified during line and load regulation tests.

- 3. Guaranteed for a D.C. to 20MHz bandwidth. Tested using a 20KHz to 10MHz bandwidth.

- 4. Capacitive load may be any value from 0 to the maximum limit without compromising dc performance.

A capacitive load in excess of the maximum limit may interfere with the proper operation of the converter's overload protection, causing erratic behavior during turn-on.

- Överload power dissipation is defined as the device power dissipation with the load set such that both outputs are in a short circuit mode.

- 6. Load step transition time  $\leq$  10 µsec.

- Recovery time is measured from the initiation of the transient to where V<sub>OUT</sub> has returned to within ±1% of its steady state value.

- 8. Line step transition time ≤100 µsec.

- 9. Turn-on delay time from either a step application of input power or a logic low to a logic high transition on the inhibit pin (pin 6) to the point where V<sub>OUT</sub> = 90% of nominal.

- 10. Current limit point expressed as a percentage of full rated load current.

- 11. For models with two positive outputs the envelope specification for the design is that each output voltage is limited to the range 1V to 5V.

- 12. Although operation at temperatures between +85°C and +125°C is guaranteed, no parameter limits are specified.

- 13. Meets the derating requirements of EEE-INST-002 except for ceramic capacitors with voltage stress below 10V will minimum be rated at 50V and a minimum load of 20mA on each output.

## **Device Screening**

| Test / Inspection          | Method                                    | /EM Suffix  | Flight (No Suffix) |

|----------------------------|-------------------------------------------|-------------|--------------------|

| Element Evaluation         | MIL-STD-38534 Class K equivalent with SEM | N/A         | X                  |

| Nondestructive Bond Pull   | MIL-STD-883, Method 2023                  | N/A         | Х                  |

| Internal Visual            | MIL-STD-883, Method 2017                  | Note 1      | X                  |

| Temperature Cycling        | MIL-STD-883, Method 1010                  | N/A         | Condition C        |

| Constant Acceleration      | MIL-STD-883, Method 2001, Y1 Axis         | N/A         | 3000 G's           |

| PIND                       | MIL-STD-883, Method 2020                  | N/A         | Α                  |

| Burn-in (2 x 220 hours)    | MIL-STD-883, Method 1015                  | 48 Hours    | 440 Hours          |

|                            |                                           | @ 115°C     | @ 115°C            |

| Final Electrical (Group A) | In accordance with device specification   | Х           | Х                  |

| Seal                       | MIL-STD-883, Method 1014                  | Condition A |                    |

| Fine Leak                  |                                           |             | A1                 |

| Gross Leak                 |                                           |             | С                  |

| Radiographic               | MIL-STD-883, Method 2012                  | N/A         | N/A                |

| External Visual            | MIL-STD-883, Method 2009                  | Note 1      | Yes                |

#### Notes:

#### **Radiation Performance Characteristics**

| Test                          | Conditions                                                         | Min | Unit                    |

|-------------------------------|--------------------------------------------------------------------|-----|-------------------------|

| Total Ionizing Dose (Gamma) * | MIL-STD-883, Method 1019.5 Operating bias applied during exposure, | 50  | KRads (Si)              |

| Total fortizing bose (danima) | Full Rated Load, VIN = 50V                                         | 3   | randa (Oi)              |

|                               | Heavy Ions (LET)                                                   |     |                         |

| Single Event Effects *        | Operating bias applied during exposure,                            | 40  | MeV•cm <sup>2</sup> /mg |

| SEU, SEL, SEGR, SEB           | Full Rated Load, VIN = 26, 42, 55V                                 |     |                         |

<sup>\*</sup> Test performed at TAMU

International Rectifier currently does not have a DSCC certified Radiation Hardness Assurance Program.

<sup>1.</sup> Best commercial practice

Fig. 1 - EMI Conducted Emission Performance Limit

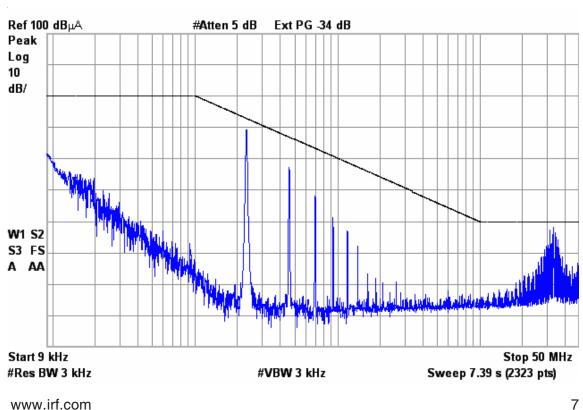

Fig. 2 - A Typical input EMI Conducted Emission Performance

## **Mechanical Outline - Option A (Straight Pins)**

## **Mechanical Outline - Option B (Down Pins)**

#### **Block Diagram** Output 1 Rectifier Rectifier Linear & Filter & Filter Internal Reg Output 1 Supply RTN Output 1 Inhibit Input Power Input Filter Stage Input Return 316 Rectifier Vaux& Start up Vref Filter resistor Case Output 2 Inhibit Sync In Output 2 Rectifier RIN PWM Current Linear Sync Out 5 & Control Sense Reg Filter Output 2 In hi bit

## **Pin Designation**

| Pin # | Р                       |  |

|-------|-------------------------|--|

|       | (Both Outputs Positive) |  |

| 1     | Input                   |  |

| 2     | Input Return            |  |

| 3     | Case                    |  |

| 4     | Sync In                 |  |

| 5     | Sync Out                |  |

| 6     | Inhibit                 |  |

| 7     | Output 2                |  |

| 8     | Output 2 Return         |  |

| 9     | Output 2 Inhibit        |  |

| 10    | Output 1 Inhibit        |  |

| 11    | Output 1 Return         |  |

| 12    | Output 1                |  |

Note: Pins 8 and 11 are internally connected

WORLD HEADQUARTERS: 101 N, Sepulveda Blvd., El Segundo, California 90245, USA Tel: (310) 252-7105 IR SAN JOSE: 2520 Junction Avenue, San Jose, California 95134, USA Tel: (408) 434-5000 Visit us at www.irf.com for sales contact information.

Data and specifications subject to change without notice. 05/2013